JUNE 2007

### **GENERAL DESCRIPTION**

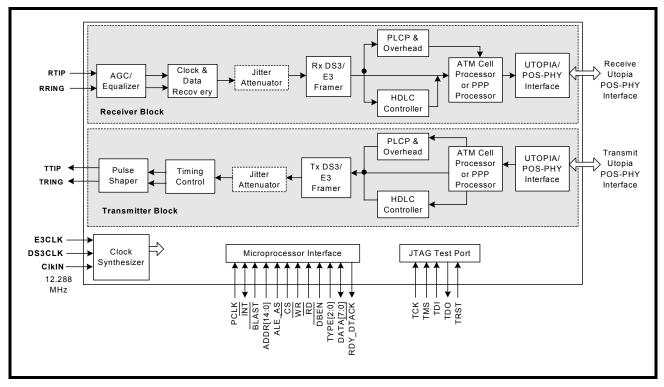

The XRT79L71 is a single channel, ATM UNI/PPP Physical Layer Processor with integrated DS3/E3 framing controller and Line Interface Unit with Jitter Attenuator that is designed to support ATM direct mapping and cell delineation as well as PPP mapping and Frame processing. For ATM UNI applications, this device provides the ATM Physical Layer (Physical Medium Dependent and Transmission Convergence sub-layers) interface for the public and private networks at DS3/E3 rates. For Clear-Channel Framer applications, this device supports the transmission and reception of "user data" via the DS3/E3 payload.

The XRT79L71 includes DS3/E3 Framing, Line Interface Unit with Jitter Attenuator that supports mapping of ATM or HDLC framed data. A flexible parallel microprocessor interface is provided for configuration and control. Industry standard UTOPIA II and POS-PHY interface are also provided.

#### GENERAL FEATURES:

- Integrated T3/E3 Line Interface Unit

- Integrated Jitter Attenuator that can be selected either in Receive or Transmit path

- Flexible integrated Clock Multiplier that takes single frequency clock and generates either DS3 or E3 frequency.

- 8/16 bit UTOPIA Level I and II and PPP Multi-PHY Interface operating at 25, 33 or 50 MHz.

- HDLC Controller that provides the mapping/ extraction of either bit or byte mapped encapsulated packet from DS3/E3 Frame.

- Contains on-chip 16 cell FIFO (configurable in depths of 4, 8, 12 or 16 cells), in both the Transmit (TxFIFO) and Receive Directions (RxFIFO)

- Contains on-chip 54 byte Transmit and Receive OAM Cell Buffer for transmission, reception and processing of OAM Cells

- Supports ATM cell or PPP Packet Mapping

- Supports M13 and C-Bit Parity Framing Formats

- Supports DS3/E3 Clear-Channel Framing.

- Includes PRBS Generator and Receiver

- Supports Line, Cell, and PLCP Loop-backs

- Interfaces to 8 Bit wide Intel, Motorola, PowerPC, and Mips µPs

- Low power 3.3V, 5V Input Tolerant, CMOS

- Available in 208 STBGA Package

- JTAG Interface

#### LINE INTERFACE UNIT

- On chip Clock and Data Recovery circuit for high input jitter tolerance

- Meets E3/DS3 Jitter Tolerance Requirements

- Detects and Clears LOS as per G.775.

- Receiver Monitor mode handles up to 20 dB flat loss with 6 dB cable attenuation

- Compliant with jitter transfer template outlined in ITU G.751, G.752, G.755 and GR-499-CORE,1995 standards

- Meets ETSI TBR 24 and GR-499 Jitter Transfer Requirements

- On chip B3ZS/HDB3 encoder and decoder that can be either enabled or disabled

- On-chip clock synthesizer provides the appropriate rate clock from a single 12.288 MHz Clock

- On chip advanced crystal-less Jitter Attenuator

- Jitter Attenuator can be selected in Receive or Transmit paths

- 16 or 32 bits selectable FIFO size

- Meets the Jitter and Wander specifications described in T1.105.03b,ETSI TBR-24, Bellcore GR-253 and GR-499 standards

- Jitter Attenuator can be disabled

- Typical power consumption 1.3W

#### **DS3/E3 FRAMER**

- DS3 framer supports both M13 and C-bit parity.

- DS3 framer meets ANSI T1.107 and T1.404 standards.

- Detects OOF,LOF,AIS,RDI/FERF alarms.

- Generation and Insertion of FEBE on received parity errors supported.

- Automatic insertion of RDI/FERF on alarm status.

- E3 framer meets G.832,G.751 standards.

- Framers can be bypassed.

#### ATM/PPP PROTOCOL PROCESSOR

#### TRANSMIT CELL PROCESSING

• Extracts ATM cells

### 1-CHANNEL DS3/E3 ATM UNI/PPP/CLEAR-CHANNEL FRAMER IC - REGISTER/MAP DESCRIPTION

- Supports ATM cell payload scrambling

- Maps ATM cells into E3 or DS3 frame

- PLCP frame and mapping of ATM cell streams

### RECEIVE CELL PROCESSING

- Extraction of ATM cells from PLCP frame or directly from E3 or DS3 frame

- Termination of PLCP frame

- Supports payload cell de-scrambling

### TRANSMIT PACKET PROCESSING

- Inserts PPP packets into data stream

- Maps HDLC data stream directly into DS3 or E3 frame

- Extracts in-band messaging packets

- Supports CRC-16/32, HDLC flag and Idle sequence generation

### **RECEIVE PACKET PROCESSING**

- Extracts HDLC data stream from DS3 or E3 frame

- Inserts in-band messaging packets

### FIGURE 1. BLOCK DIAGRAM OF THE XRT79L71

• Detects and removes HDLC flags

### **UTOPIA/ SYSTEM INTERFACE**

- 8/16 bit UTOPIA Level I and II and PPP Multi-PHY Interface operating at 25, 33 or 50 MHz.

- Compliant with ATM Forum UTOPIA II interface

- Programmable FIFO size for both Transmit and Receive direction

- Compliant to POS-PHY Level 2 interface

### SERIAL INTERFACE

- Serial clock and data interface for accessing DS3/ E3 framer

- Serial clock and data interface for accessing cell/ packet processor

### APPLICATIONS

- Digital Access and Cross Connect Systems

- 3G Base Stations

- DSLAMs

- Digital, ATM, WAN and LAN Switches

REV. 1.0.0

REV. 1.0.0 1-CHANNEL DS3/E3 ATM UNI/PPP/CLEAR-CHANNEL FRAMER IC - REGISTER/MAP DESCRIPTION

### **PRODUCT ORDERING INFORMATION**

| PRODUCT NUMBER | PACKAGE TYPE                                  | OPERATING TEMPERATURE RANGE |

|----------------|-----------------------------------------------|-----------------------------|

| XRT79L71IB     | 17X17 mm 208 Ball Shrink Thin Ball Grid Array | -40°C to +85°C              |

### TABLE 1: PIN OUT OF THE XRT79L71 (TOP VIEW)

| A | RXGFCCLK   | RXPLOF     | TXPOHFRAME | RXNIB_2                         | RXSER     | RXCLK      | RXOHCLK                          | RXOHFRAME | TXNIB_0  | TXNIBFRAME | TXFRAMEREF | TXOHENABLE | TXAISEN  | PDATA_3  | PDATA_7  | PAS_L      |

|---|------------|------------|------------|---------------------------------|-----------|------------|----------------------------------|-----------|----------|------------|------------|------------|----------|----------|----------|------------|

| В | RXGFCMSB   | RXPRED     | TXPOHCLK   | RXNIB_3                         | RXOUTCLK  | RXFRAME    | RXOHENABLE                       | TXNOB_3   | TXOHIND  | TXFRAME    | TXOHFRAME  | TXOHCLK    | PDATA_2  | PDATA_6  | PBLAST_L | PWR_L      |

| c | RXUDATA_13 | TXGFCCLK   | RXGFC      | RXPOHFRAME                      | RXNIB_0   | RXOHIND    | RXOH                             | TXNOB_2   | TXSER    | TXINCLK    | тхон       | PDATA_1    | PDATA_5  | PRDY_L   | PRD_L    | PADDR_0    |

| D | RXUDATA_9  | RXUDATA_12 | RXUDATA_15 | RXCP                            | RXPOOF    | RXNIB_1    | RXLOS                            | TXNIB_1   | TXNIBCLK | TXOHINS    | PDATA      | PDATA_4    | PINT_L   | PCS_L    | PADDR_1  | PADDR_2    |

| Ш | RXUDATA_5  | RXUDATA_8  | RXUDATA_11 | RXUDATA_14                      |           |            |                                  |           |          |            |            |            | PADDR_6  | PADDR_5  | PADDR_4  | PADDR_3    |

| ш | RXUDATA_2  | RXUDATA_4  | RXUDATA_7  | RXUDATA_6 RXUDATA_10 RXUDATA_14 |           |            |                                  |           |          |            | _          |            | 0PADDR_3 | DPADDR_2 | DPADDR_1 | DPADDR_0   |

| ი | RXUDATA_1  | RXUDATA_0  | RXUDATA_3  | RXUDATA_6                       |           |            | Dav                              | DDV       | DDV      | DDV        |            |            | DPADDR_7 | DPADDR_6 | DPADDR_5 | DPADDR_4   |

| т | RXUCLAV    | RXUSOC     | RXUPRTY    | RXUEN_L                         |           |            | GND                              | GND       | GND      | GND        |            |            | DA_SEL   | DD       | GND      | PCLK       |

| ſ | RXUADDR_0  | RXUADDR_1  | RXUADDR_2  | RXUADDR_3                       |           |            | GND                              | GND       | GND      | GND        |            |            | PDBEN_L  | PTYPE_2  | PTYPE_1  | PTYPE_0    |

| х | RXUADDR_4  | RXUCLKO    | RXPEOP     | RSX_RSOF                        |           |            | Dav                              | DDV       | DDV      | DOV        |            |            | GP0_2    | GP0_1    | GPO_0    | СГКОИТ     |

| L | RXMOD      | RXPERR     | RXUCLK     | TSX_TSOF                        |           |            |                                  |           |          |            | -          |            | GPI_2    | GPI_1    | GPI_0    | NIBBLEINTF |

| Μ | TXUCLK     | тхрек      | TXMOD      | TXUEN_L                         |           |            |                                  |           |          |            |            |            | OGND     | RESET_L  | TESTMODE | E3CLK      |

| z | TXPEOP     | RXPDVAL    | TXUCLAV    | TXUDATA_10                      | TXUDATA_4 | TXUDATA_8  | TXUDATA_13                       | GPI0_1    | TDO      | TXDGND     | TXDVDD     | TXAGND     | OVDD     | DQV      | GND      | CLKGND     |

| Р | TXUCLKO    | TXUADDR_4  | TXUSOC     | TXUDATA_1                       | TXUDATA_5 | TXUDATA_9  | TXUDATA_15 TXUDATA_14 TXUDATA_13 | GPIO_2    | TDI      | MTIP       | MRING      | REFAGND    | ANAIO1   | ANAIO2   | ICTB     | DS3CLK     |

| Я | TXUADDR_3  | TXUADDR_2  | тхиряту    | TXUDATA_2                       | TXUDATA_6 | TXUDATA_11 | TXUDATA_15                       | GPI0_3    | TMS      | TRST       | NC         | REFAVDD    | RRING    | RTIP     | TXON     | CLKVDD     |

REV. 1.0.0

1-CHANNEL DS3/E3 ATM UNI/PPP/CLEAR-CHANNEL FRAMER IC - REGISTER/MAP DESCRIPTION

|   |           |           |           |          |           |            |        |       |     | •     |     |          |        |        |       |        |

|---|-----------|-----------|-----------|----------|-----------|------------|--------|-------|-----|-------|-----|----------|--------|--------|-------|--------|

| ⊢ | TXUADDR_1 | TXUADDR_0 | TXUDATA_0 | TXUDAT_3 | TXUDATA_7 | TXUDATA_12 | GPIO_0 | 0_OMO | тск | TRING | ЫЛТ | DUTXAVDD | RXAVDD | RXAGND | JAGND | JAAVDD |

|   | -         | 2         | 3         | 4        | 5         | 6          | 7      | 8     | 6   | 10    | 11  | 12       | 13     | 14     | 15    | 16     |

REV. 1.0.0 1-CHANNEL DS3/E3 ATM UNI/PPP/CLEAR-CHANNEL FRAMER IC - REGISTER/MAP DESCRIPTION

# TABLE OF CONTENTS

| GENERAL DESCRIPTION                                                                   | . 1  |

|---------------------------------------------------------------------------------------|------|

| GENERAL FEATURES:                                                                     | 1    |

| Line Interface Unit                                                                   |      |

| DS3/E3 Framer                                                                         |      |

| ATM/PPP Protocol Processor                                                            |      |

| Transmit Cell Processing                                                              |      |

| Receive Cell Processing                                                               |      |

| Transmit Packet Processing                                                            |      |

| Receive Packet Processing<br>Utopia/ System Interface                                 |      |

| Serial Interface                                                                      |      |

| APPLICATIONS.                                                                         |      |

| FIGURE 1. BLOCK DIAGRAM OF THE XRT79L71                                               |      |

| PRODUCT ORDERING INFORMATION                                                          |      |

| TABLE 1: PIN OUT OF THE XRT79L71 (TOP VIEW)                                           |      |

| TABLE OF CONTENTS                                                                     |      |

| 1.0 BRIEF XRT79L71 ARCHITECTURE DESCRIPTION (SEE 79L71 PRODUCT BRIEF)                 | 5    |

| 2.0 INTERRUPT STRUCTURE WITHIN THE XRT79L71 (SEE 79L71 PRODUCT BRIEF)                 |      |

| 3.0 REGISTER MAP/DESCRIPTION OF THE XRT79L71 1-CHANNEL DS3/E3 ATM UNI/PPP/CLEAR-      |      |

| CHANNEL FRAMER WITH LIU IC                                                            |      |

| COMMONCONTROL REGISTERS OF THE XRT79L71                                               |      |

| Channel Control Registers.                                                            |      |

| Channel Control Registers                                                             |      |

| LIU/JITTER ATTENUATOR CONTROL REGISTERS                                               |      |

| RECEIVE ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REGISTERS                      |      |

| TRANSMIT ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REGISTERS                     |      |

| OPERATION BLOCK INTERRUPT REGISTER BIT FORMATS                                        |      |

|                                                                                       |      |

|                                                                                       |      |

|                                                                                       |      |

|                                                                                       | -    |

|                                                                                       | -    |

|                                                                                       |      |

|                                                                                       |      |

|                                                                                       | -    |

|                                                                                       | -    |

|                                                                                       | -    |

|                                                                                       |      |

| CHANNEL INTERRUPT INDICATION REGISTERS                                                | 32   |

|                                                                                       | 32   |

|                                                                                       | 32   |

|                                                                                       | 33   |

|                                                                                       | 33   |

|                                                                                       | 34   |

|                                                                                       | 36   |

| <b>RECEIVE UTOPIA INTERFACE BLOCK - ATM UNI APPLICATIONS</b>                          | 39   |

| TABLE 2: RECEIVE UTOPIA INTERFACE BLOCK - REGISTER/ADDRESS MAP - ATM UNI APPLICATIONS | . 39 |

|                                                                                       | 40   |

|                                                                                       | 43   |

|                                                                                       | 43   |

| THE RECEIVE POS-PHY INTERFACE BLOCK - PPP APPLICATIONS                                | 45   |

| RECEIVE POS-PHY INTERFACE BLOCK - REGISTER/ADDRESS MAP - PPP APPLICATIONS             |      |

|                                                                                       |      |

|                                                                                       | 47   |

| ANSMIT UTOPIA INTERFACE BLOCK - ATM UNI APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CHANNEL DS3/E3 ATM UNI/PPP/CLEAR-CHANNEL FRAMER IC - REGISTER/MAP DESCRIPTION | REV. 1.        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------|

| TABLE 3: TRANSMIT UTOPIA INTERFACE BLOCK - REGISTER/ADDRESS MAP - ATM UNI APPLICATIONS         E TRANSMIT POS-PHY INTERFACE BLOCK - REGISTER/ADDRESS MAP - PPP APPLICATIONS         TABLE 4: TRANSMIT POS-PHY INTERFACE BLOCK - REGISTER/ADDRESS MAP - PPP APPLICATIONS         SJE3 FRAMER AND PLCP PROCESSOR BLOCK REGISTERS         SJE3 FRAMER BLOCK REGISTERS         SJE3 FRAMER BLOCK REGISTERS         RECEIVE DS3 RELATED REGISTERS         RECEIVE E3, ITU-T G. 751 RELATED REGISTERS         RECEIVE E3, ITU-T G. 751 RELATED REGISTERS         1         RECEIVE E3, ITU-T G. 832 RELATED REGISTERS         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 </td <td></td> <td>5</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               | 5              |

| TABLE 3: TRANSMIT UTOPIA INTERFACE BLOCK - REGISTER/ADDRESS MAP - ATM UNI APPLICATIONS         E TRANSMIT POS-PHY INTERFACE BLOCK - REGISTER/ADDRESS MAP - PPP APPLICATIONS         TABLE 4: TRANSMIT POS-PHY INTERFACE BLOCK - REGISTER/ADDRESS MAP - PPP APPLICATIONS         SJE3 FRAMER AND PLCP PROCESSOR BLOCK REGISTERS         SJE3 FRAMER BLOCK REGISTERS         SJE3 FRAMER BLOCK REGISTERS         RECEIVE DS3 RELATED REGISTERS         RECEIVE E3, ITU-T G. 751 RELATED REGISTERS         RECEIVE E3, ITU-T G. 751 RELATED REGISTERS         1         RECEIVE E3, ITU-T G. 832 RELATED REGISTERS         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 </td <td>RANSMIT UTOPIA INTERFACE BLOCK - ATM UNI APPLICATIONS</td> <td>5</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RANSMIT UTOPIA INTERFACE BLOCK - ATM UNI APPLICATIONS                         | 5              |

| E TRANSMIT POS-PHY INTERFACE - PPP APPLICATIONS TABLE 4: TRANSMIT POS-PHY INTERFACE BLOCK - REGISTER/ADDRESS MAR - PPP APPLICATIONS 3/E3 FRAMER AND PLCP PROCESSOR BLOCK REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                               | -              |

| E TRANSMIT POS-PHY INTERFACE - PPP APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                               |                |

| E TRANSMIT POS-PHY INTERFACE - PPP APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                               | 5              |

| TABLE 4: TRANSMIT POS-PHY INTERFACE BLOCK - REGISTER/ADDRESS MAP - PPP APPLICATIONS         I3/E3 FRAMER AND PLCP PROCESSOR BLOCK REGISTERS         IS/E3 FRAMER BLOCK REGISTERS         SPECEIVE DS3 RELATED REGISTERS         RECEIVE E3, ITU-T G.751 RELATED REGISTERS         RECEIVE E3, ITU-T G.751 RELATED REGISTERS         RECEIVE E3, ITU-T G.751 RELATED REGISTERS         RECEIVE E3, ITU-T G.832 RELATED REGISTERS         RECEIVE E3, ITU-T G.833 RELATED REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                               | 5              |

| TABLE 4: TRANSMIT POS-PHY INTERFACE BLOCK - REGISTER/ADDRESS MAP - PPP APPLICATIONS         I3/E3 FRAMER AND PLCP PROCESSOR BLOCK REGISTERS         IS/E3 FRAMER BLOCK REGISTERS         SPECEIVE DS3 RELATED REGISTERS         RECEIVE E3, ITU-T G.751 RELATED REGISTERS         RECEIVE E3, ITU-T G.751 RELATED REGISTERS         RECEIVE E3, ITU-T G.751 RELATED REGISTERS         RECEIVE E3, ITU-T G.832 RELATED REGISTERS         RECEIVE E3, ITU-T G.833 RELATED REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | HE TRANSMIT POS-PHY INTERFACE - PPP APPLICATIONS                              | 5              |

| 3/E3 FRAMER AND PLCP PROCESSOR BLOCK REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                               |                |

| 3/E3 FRAMER BLOCK REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                               |                |

| 3/E3 FRAMER BLOCK REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                               | 5              |

| DS/E3 FRAMER BLOCK REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                               | 6              |

| DS/E3 FRAMER BLOCK REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | S3/E3 FRAMER AND PLCP PROCESSOR BLOCK REGISTERS                               | 6              |

| RECEIVE DS3 RELATED REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                               |                |

| RECEIVE DS3 RELATED REGISTERS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                               |                |

| RECEIVE DS3 RELATED REGISTERS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                               | -              |

| RECEIVE E3, ITU-T G.751 RELATED REGISTERS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                               |                |

| RECEIVE E3, ITU-T G.751 RELATED REGISTERS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                               | -              |

| Receive E3, ITU-T G.751 Related Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                               |                |

| RECEIVE E3, ITU-T G.751 RELATED REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |                |

| RECEIVE E3, ITU-T G.751 RELATED REGISTERS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                               |                |

| RECEIVE E3, ITU-T G.751 RELATED REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |                |

| RECEIVE E3, ITU-T G.751 RELATED REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |                |

| Receive E3, ITU-T G.751 Related Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |                |

| RECEIVE E3, ITU-T G.751 RELATED REGISTERS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                               |                |

| RECEIVE E3, ITU-T G.751 RELATED REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |                |

| RECEIVE E3, ITU-T G.751 RELATED REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |                |

| Image: State in the state |                                                                               |                |

| RECEIVE E3, ITU-T G.832 RELATED REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RECEIVE E3, ITU-T G.751 RELATED REGISTERS                                     |                |

| RECEIVE E3, ITU-T G.832 RELATED REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               | 8              |